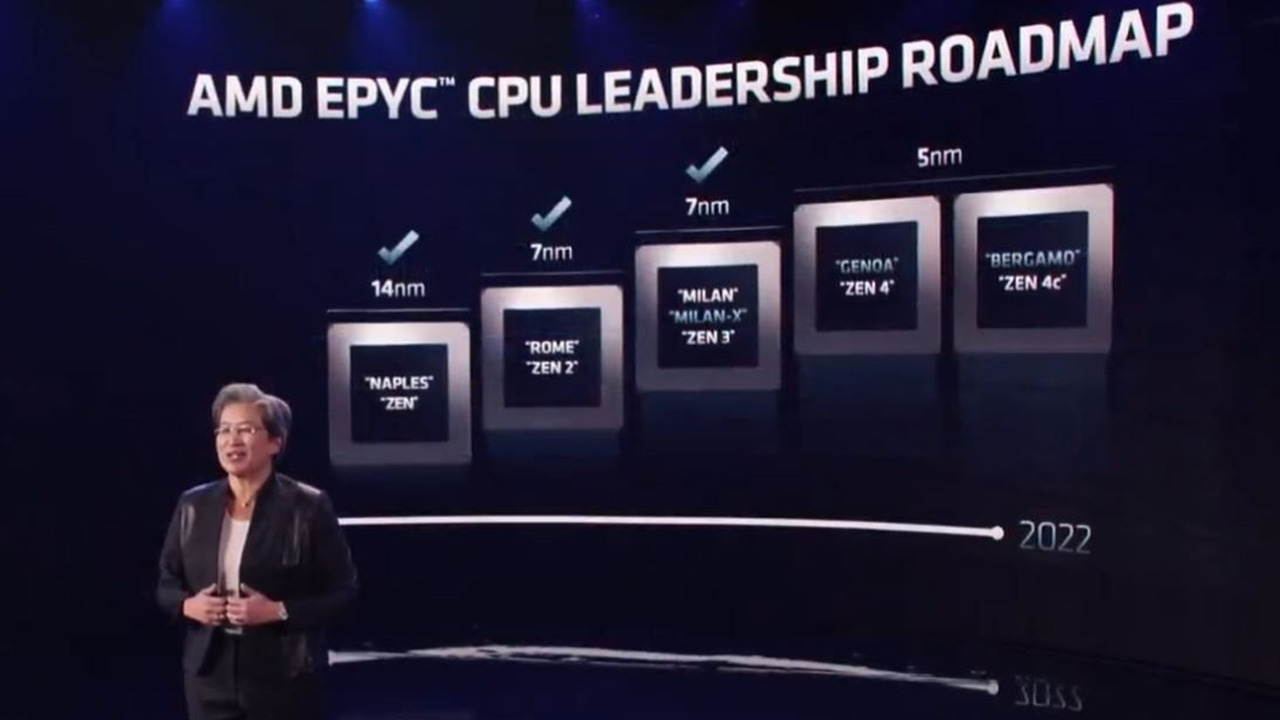

Tại sự kiện AMD Accelerated Data Center, Giám đốc điều hành AMD Lisa Su đã chia sẻ lộ trình CPU Zen 4 của công ty, bao gồm mẫu Genoa 96 lõi và chip Bergamo 128 lõi.

AMD cũng đã chia sẻ chi tiết đầu tiên về quy trình TSMC 5nm mà họ sẽ sử dụng cho chip Genoa và Bergamo mới, tuyên bố rằng nó cung cấp mật độ và hiệu suất năng lượng cao gấp đôi cùng với hiệu suất cao hơn 1,25 lần so với quy trình 7nm mà AMD đang sử dụng cho các chip thế hệ hiện tại của mình.

Lộ trình mới bao gồm các bộ xử lý EYPC thế hệ thứ tư. Genoa 96 lõi sẽ sử dụng quy trình 5nm vào năm 2022, trong khi Bergamo 128 lõi, cũng trên quy trình 5nm, sẽ ra mắt thị trường vào năm 2023.

Ngoài ra, Bergamo còn đi kèm với một loại lõi ‘Zen 4c’ mới được tối ưu hóa cho các các trường hợp sử dụng, nghĩa là chip Zen 4 của AMD sẽ có hai loại lõi, với lõi ‘c’ rõ ràng là các biến thể nhỏ hơn.

Sau đây là tóm tắt ngắn gọn lộ trình của AMD cho CPU Zen 4:

- “Genoa” sẽ có tới 96 lõi “Zen 4” hiệu năng cao, triển khai thế hệ bộ nhớ và công nghệ I/O tiếp theo trong DDR5 và PCIe Gen 5 và khả năng nền tảng ổ đĩa cân bằng hoàn hảo giữa lõi Zen 4, bộ nhớ và I/O để mang lại hiệu suất lãnh đạo

- “Bergamo” là một công cụ tính toán số lõi cao, được tùy chỉnh cho các ứng dụng gốc đám mây yêu cầu mật độ luồng mật độ cao. Có 128 lõi “Zen 4 C” hiệu suất cao

- “Bergamo” có tất cả các tính năng tương tự như Genoa bao gồm, DDR5, PCIe 5, CXL 1.1, cùng một RAS và bộ đầy đủ các tính năng bảo mật của Infinity Guard và nó tương thích với socket của Genoa

Genoa sẽ có quy trình 5nm từ TSMC và AMD cho biết 5nm có khả năng tiết kiệm năng lượng cao gấp đôi so với quy trình 7nm cung cấp năng lượng cho chip EPYC Milan thế hệ hiện tại.

Không chỉ vậy, hiệu suất của 5nm cũng cao gấp 1,25 lần hiệu suất của quy trình 7nm. Điều này báo hiệu tốt cho các chip Ryzen Zen 4 tập trung vào người tiêu dùng.

Các chip EPYC Genoa sẽ có tới 96 lõi Zen 4 và hỗ trợ DDR5 và PCIe 5.0, cùng với giao diện CXL 1.1 cho phép kết nối bộ nhớ chặt chẽ giữa các thiết bị.

Con chip này sẽ giải quyết khối lượng công việc của HPC và trung tâm dữ liệu mục đích chung, doanh nghiệp và đám mây. Bà Lisa Su cho biết nó sẽ mở rộng cả hiệu suất trên mỗi lõi và mức ổ cắm (đa luồng). Genoa chuẩn bị ra mắt vào năm 2022.

Bergamo cũng được sản xuất trên quy trình 5nm và sẽ có tới 128 lõi trong một con chip.

AMD đã tạo ra loại lõi Zen 4 mới ‘Zen 4c’, với chữ ‘c’ biểu thị rằng lõi này được thiết kế cho khối lượng công việc gốc đám mây.

Các lõi Zen 4c ra mắt trong EPYC Bergamo 5nm, tương thích với socket của Genoa và sử dụng cùng một tập lệnh Zen 4. Điều đó có nghĩa là bạn có thể thả các chip này vào các máy chủ giống như các mô hình Genoa.

Các lõi ‘c’ này có thể nhỏ hơn lõi Zen 4 tiêu chuẩn sẽ ra mắt tại Genoa, với một số chức năng không cần thiết nhất định bị loại bỏ để cải thiện mật độ tính toán.

Tuy nhiên, các chip có hệ thống phân cấp bộ nhớ cache được tối ưu hóa mật độ để tăng số lượng lõi, do đó giải quyết khối lượng công việc đám mây yêu cầu mật độ luồng cao hơn. Điều này có thể có nghĩa là các chip có các bộ nhớ cache nhỏ hơn hoặc có lẽ mức bộ nhớ cache đã bị tháo, nhưng AMD chưa chia sẻ chi tiết.

AMD nói rằng Bergamo sẽ cung cấp mức hiệu suất và hiệu suất năng lượng cao hơn trên mỗi ổ cắm. Bergamo sẽ xuất xưởng vào nửa đầu năm 2023 và nó sẽ đi kèm với bộ tính năng tổng thể giống như Genoa, vì vậy nó có PCIe 5.0, DDR5 và CXL 1.1.

Cũng trong sự kiện Accelerated Data Center này, AMD đã công bố dòng sản phẩm GPU điện toán AMD Instinct MI200 với thiết kế chiplet với sức mạnh tính toán tổng cộng lên đến 96TFLOPS với dấu chấm động 64bit, mạnh gần gấp 5 lần mẫu chip điện toán A100 đến từ NVIDIA.

Đây là phiên bản nâng cấp của dòng sản phẩm Instinct từ phiên bản MI100 với kiến trúc CDNA2 hoàn toàn mới, sản xuất trên quy trình công nghệ TSMC N6, là phiên bản nâng cấp nhẹ của quy trình N7 đang được sử dụng hiện nay.